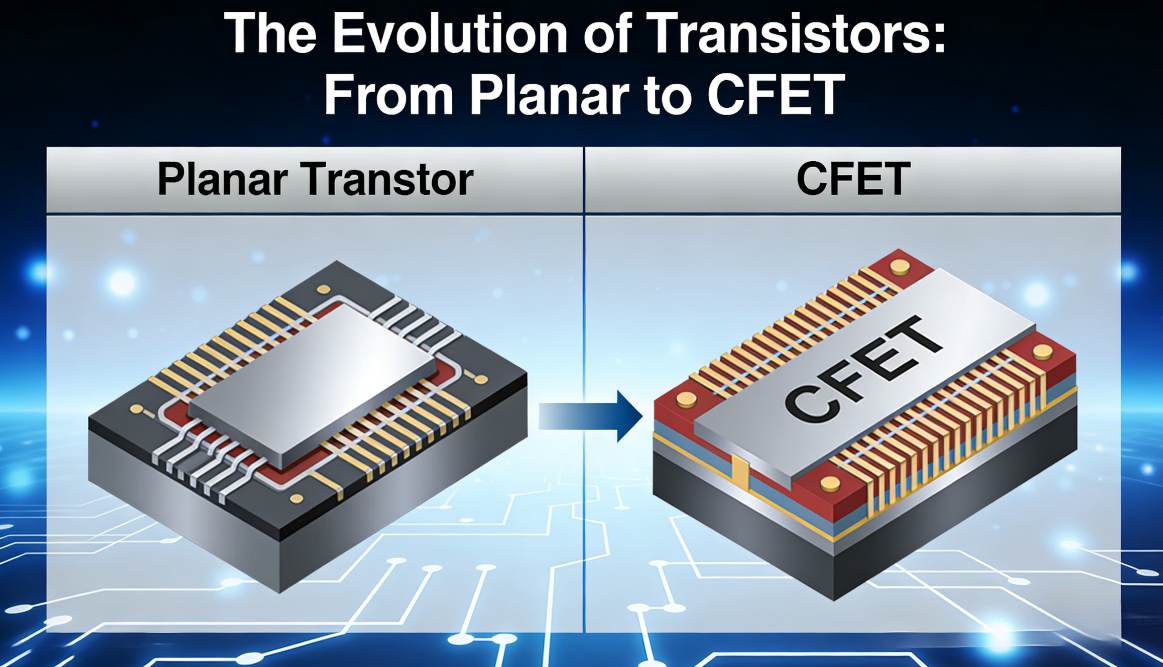

Evolusi Transistor: Dari Planar ke CFET, Integrasi 3D Mendefinisikan Ulang Kemajuan Semikonduktor

Selama lebih dari setengah abad, industri semikonduktor tumbuh dengan mengikuti satu aturan sederhana: memperkecil transistor.Ukuran fitur yang diperkecil menghasilkan kinerja yang lebih tinggi, daya yang lebih rendah, dan biaya per transistor yang lebih rendah.Namun saat ini, jalur tersebut telah mencapai batas fisik dan ekonominya.Era penskalaan murni telah berakhir, dan era baru telah berakhir inovasi struktural dan integrasi 3D telah dimulai.

Transistor itu sendiri sedang mengalami revolusi arsitektur yang lengkap.Dari MOSFET planar hingga FinFET, dari nanosheet GAA hingga penumpukan CFET, setiap langkah mewakili peralihan dari penyusutan ke membangun kembali transistor dalam tiga dimensi.Ini bukan sekadar peningkatan bertahap—ini adalah pendefinisian ulang menyeluruh tentang bagaimana chip menghasilkan kinerja.

Empat Generasi Arsitektur Transistor

1. Transistor Planar (2D Tradisional)

Struktur datar klasik, di mana gerbang mengontrol saluran dari atas.Ini mendominasi dari awal hingga 40nm dan 28nm.Ketika dimensi semakin menyusut, arus bocor dan kontrol elektrostatis menjadi masalah yang tidak dapat diselesaikan.

2. FinFET (Kontrol Gerbang 3D)

Saluran tersebut menjadi “sirip” vertikal, dengan gerbang melingkari ketiga sisinya.Hal ini secara drastis meningkatkan kontrol elektrostatis, mengurangi kebocoran, dan memungkinkan penurunan skala hingga 7nm, 5nm, dan bahkan 3nm.FinFET menjadi fondasi era chip modern berperforma tinggi.

3. GAA Nanosheet (Gerbang Serba Ada)

Pada 2nm ke bawah, FinFET mencapai batasnya.GAA menggantikan sirip dengan tumpukan kawat nano atau lembaran horizontal, dikelilingi sepenuhnya oleh gerbang.Ini memberikan kontrol yang lebih baik, daya yang lebih rendah, dan arus penggerak yang lebih tinggi.GAA kini menjadi struktur utama untuk chip kelas 2nm di TSMC, Samsung, dan Intel.

4. CFET (FET Pelengkap)

Perbatasan berikutnya: menumpuk NMOS dan PMOS secara vertikal.CFET menggabungkan dua transistor menjadi satu transistor, sehingga secara drastis mengurangi area dan meningkatkan kepadatan.Ini adalah akhir evolusi akhir dari penskalaan transistor sebelum integrasi sistem 3D yang sebenarnya mengambil alih.

Mengapa Penskalaan Sendiri Tidak Lagi Berfungsi

- Biaya proses meningkat secara eksponensial di setiap node baru

- Kebocoran kuantum dan kendala fisik memperkeras batas

- Penundaan interkoneksi dan konsumsi daya melampaui kecepatan transistor

- Keripik monolitik besar memiliki hasil yang rendah dan biaya tinggi

Industri telah menyadari: kinerja tidak lagi berasal dari transistor yang lebih kecil.Itu berasal dari koneksi yang lebih baik, arsitektur yang lebih cerdas, dan integrasi vertikal.

Era Baru: Tiga Lapisan Inovasi 3D

Kemajuan semikonduktor kini ditentukan oleh desain tiga dimensi 3D:

- Transistor 3D: FinFET, GAA, CFET – membangun transistor secara vertikal

- Penumpukan Perangkat 3D: Memori pada logika, ikatan hibrid, penumpukan SRAM

- Integrasi Sistem 3D: Chiplet, kemasan 2.5D/3D, integrasi berbasis interposer

Bersama-sama, mereka membentuk 3D×3D×3D era: transistor, perangkat, dan sistem semuanya menjadi tiga dimensi.

DTCO: Kompetensi Inti Baru

Saat penskalaan berakhir, Ko-Optimasi Teknologi Desain (DTCO) menjadi kritis.Ini berarti merancang bersama arsitektur, struktur transistor, perutean logam, dan pengemasan sejak awal.Perusahaan-perusahaan terkuat tidak lagi hanya sekedar pemimpin proses—mereka adalah integrator tingkat sistem.

Efisiensi perkabelan, penyaluran daya, desain termal, dan kepadatan bandwidth kini menentukan kinerja produk sebenarnya.

AI Adalah Kekuatan Pendorong Utama

AI dan komputasi berkinerja tinggi memerlukan bandwidth, efisiensi energi, dan kepadatan yang belum pernah ada sebelumnya.Persyaratan ini tidak dapat dipenuhi dengan penskalaan tradisional.Mereka membutuhkan:

- Interkoneksi komputasi memori dengan bandwidth ultra-tinggi

- Efisiensi energi ekstrim per operasi

- Paralelisme besar-besaran dan integrasi yang padat

AI telah memaksa seluruh industri untuk meninggalkan penskalaan murni dan menerapkan integrasi heterogen 3D penuh.

Kesimpulan: Masa Depan Bukanlah Lebih Kecil, Tapi Lebih Tinggi

Era penyusutan transistor semakin memudar.Masa depan semikonduktor bukanlah tentang membuat perangkat menjadi lebih kecil—tetapi tentang membangun sistem lebih tinggi, lebih padat, dan terhubung lebih cerdas.

Dari Planar hingga FinFET hingga GAA hingga CFET, transistor telah menyelesaikan evolusinya.Pertempuran selanjutnya akan terjadi Integrasi 3D, pengemasan canggih, dan desain tingkat sistem.Di sinilah kepemimpinan semikonduktor dekade berikutnya akan ditentukan.